# Gain Partitioning: A New Approach for Analyzing the High-Frequency Performance of Compound Semiconductor FET's

Hans-Olof Vickes, *Student Member, IEEE*

**Abstract**—A new approach for analyzing the high-frequency performance of compound semiconductor FET's is presented. The approach is based on a circuit description that separates intrinsic and parasitic circuit elements of active devices in a general way. Mason's gain ( $U$ ) and current gain ( $A_i$ ) have been used to illustrate this approach, since their unity gain frequencies,  $f_{\max}$  and  $f_{\tau}$ , respectively, are good indicators of high-frequency performance. Significant results from  $U$  have been related to a more commonly used nomenclature involving maximum stable gain (MSG) and maximum available gain (MAG) and, in particular, to the transition from a potentially unstable device to a potentially stable device. Results presented here show that the requirements to maximize these cutoff frequencies are different. Minimized parasitic circuit elements maximize  $f_{\tau}$ . A maximized  $f_{\max}$ , on the contrary, may be obtained if interactions of parasitic and intrinsic circuit elements satisfy certain conditions. The method presented here should be used in conjunction with software that can specify the physical structure required to realize those circuit elements.

## I. INTRODUCTION

THE speed with which a circuit can respond to a signal is determined by the circuit configuration as well as by the number and type of transistors and passive components in the circuit. However, regardless of the choice of circuit configuration and passive components, there are unavoidable speed limitations which depend on the transistor characteristics. It is important to know how the gain characteristics of an amplifier are related to the properties of the available transistors. Recent advances in GaAs compound semiconductor materials and improved technologies have resulted in several novel FET structures. Progress in known technologies has also enhanced, e.g., MESFET devices, allowing them to reach a performance comparable to that of AlGaAs/GaAs HEMT's and AlGaAs/InGaAs pseudomorphic HEMT's for millimeter-wave low-noise and power applications [1], [2]. These results are the first demonstration of the potential volume production of high-performance ion-implanted MESFET's for millimeter-wave application.

Useful power gain from FET's or HEMT's at high millimeter-wave frequencies is difficult to achieve. High-

frequency performance depends crucially on the fabrication process. The fabrication difficulties suggest a question: Can we manipulate the various material and structure features of the device to enhance gain performance to reach higher frequencies? Trew [3] gives an affirmative answer to this question and reports that, by varying the delay, Mason's gain near  $f_{\max}$  can be tuned to obtain an optimized performance. This observation is significant since it indicates that a minimized time delay may not be sufficient to obtain a maximized  $f_{\max}$ . It does indicate that the device structure may be optimized to obtain a tuned high-frequency response.

In addition, it was shown [5] that an increase of the charging resistance, usually denoted  $R_i$ , indicates a possible enhancement of  $f_{\max}$ . Therefore, to better understand these possible gain-frequency responses, new guidelines in high-frequency modeling are required. More precisely, since parasitic circuit elements cannot be eliminated, there is a need for powerful computer-aided methods that allow the gain of an overall FET to be predicted and analyzed in terms of an active and passive circuit description.

In this paper we present an approach that makes it possible to analyze the overall gain of the transistor and simultaneously observe the interaction of the two separated parts. An important benefit of this approach is that we may avoid introducing simplifications to the network equations. It is important to note that the concept of an equivalent circuit representation is an abstraction and a simplification of a physical device. It gives, however, a way of describing the electrical behavior of the circuit in a proper way. Therefore, once the equivalent circuit is determined, no additional simplification should be introduced. It has been shown how low-frequency approximations can result in erroneous results for high-frequency applications [3]–[5], [8].

## II. METHODS FOR PREDICTING HIGH-FREQUENCY PERFORMANCE OF COMPOUND SEMICONDUCTOR TRANSISTORS

We present here a short review of some contributions which, in this author's opinion, have had a marked influence on the progress in the high-frequency performance of transistors.

Manuscript received August 14, 1990; revised March 15, 1991.

The author was with the Electrical Engineering Department, Chalmers University of Technology, Gothenburg, Sweden. He is now with the Space Department, Ericsson Radar Electronics, Mölndal, Sweden.

IEEE Log Number 9100138.

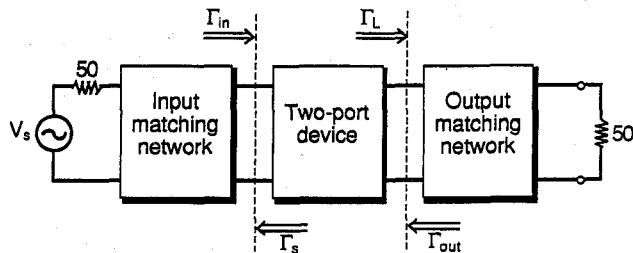

Fig. 1. Conjugate match exists when  $\Gamma_{in} = \Gamma_s^*$  and  $\Gamma_{out} = \Gamma_L^*$ .

### A. Mason's Gain

The concept of unilateral gain in linear amplifiers was treated in a classical paper by Mason [9] in 1954. The set of all nonsingular lossless reciprocal transformations forms a group in the mathematical sense. All invariants of the two-port impedance matrix,  $Z$ , under that group were found to be related to a basic invariant, which has the form

$$U = \frac{|\Delta(Z - Z^T)|}{\Delta(Z + Z^*)} = \frac{|z_{21} - z_{12}|^2}{4(r_{11}r_{22} - r_{12}r_{21})} \quad (1)$$

where  $Z^T$  is the transpose of  $Z$ ,  $Z^*$  is the complex conjugate, and  $\Delta$  is a determinant. The  $z_{ij}$  are the two-port impedance parameters of the device in question and  $r_{ij}$  is the real part of  $z_{ij}$ . The quantity  $U$  was identified by Mason as the available power gain of the resulting amplifier, whose reverse transfer impedance disappears. Therefore,  $U$  is called the unilateral gain. When  $U = 1$ , we obtain a cutoff frequency, usually denoted  $f_{\max}$ .

### B. Maximum Available Gain

A commonly used measure of amplification is the maximum available gain (MAG). For a two-port with the stability factor,  $k$ , greater than unity, it is possible to simultaneously conjugate match the two-port to produce the maximum available gain (see Fig. 1).

The maximum available gain can be written as [6]

$$\text{MAG} = \frac{|y_{21}|}{|y_{12}|} \cdot \frac{1}{k + \sqrt{k^2 - 1}} \quad (2)$$

where

$$k = \frac{2 \operatorname{Re}(y_{11}) \operatorname{Re}(y_{22}) - \operatorname{Re}(y_{12}y_{21})}{|y_{21}y_{12}|} \quad (3)$$

In order to arrive at manageable formulas expressed in the equivalent circuit parameters of a device, the MAG is calculated near the frequency limit of the transistor. With the assumption that  $k > 2$ , the MAG is usually approximated by

$$\text{MAG} \approx \frac{|y_{21}|}{|y_{12}|} \cdot \frac{1}{2k} \quad (4)$$

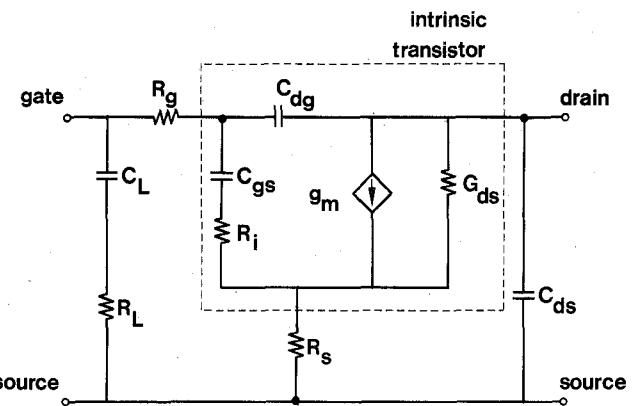

This approximate expression was used by Wolf [6]. By using the circuit topology of Fig. 2, Wolf presented a closed-form expression for the cutoff frequency  $f_{\max}$ , given

Fig. 2. Circuit elements of a Shottky barrier FET (after Wolf [6]).

Fig. 3. Equivalent circuit of an FET including parasitic elements (after Ohkawa [7]).

by

$$f_{\max} \approx \frac{1}{2\pi} \frac{g_m}{\sqrt{(4C_{gs}G_{ds}(\tau_i + \tau_s + \tau_g) + 2C_{dg}(C_{dg} + g_m(\tau_i + \tau_s + 2\tau_g)))}} \quad (5)$$

where

$$\tau_i = R_i C_{gs} \quad (6)$$

$$\tau_s = R_s C_{gs} \quad (7)$$

$$\tau_g = R_g C_{gs} \quad (8)$$

and  $\tau_i$  is the delay in the voltage-controlled current source.

It was recognized by the author that one cannot expect the expression to be accurate since the derivation contains many approximations. However, Wolf claimed that because all important elements of the equivalent circuit are incorporated, the closed-form expression can be helpful in transistor design.

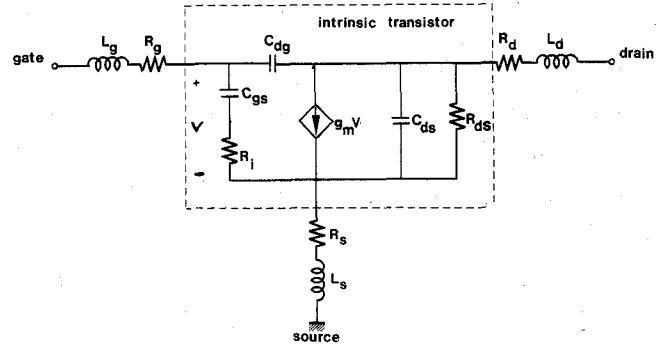

This work was further expanded by Ohkawa *et al.* [7]. By using (4) and the circuit topology of Fig. 3, they developed an approximate expression for the MAG that also included the source inductance,  $L_s$ . For the conve-

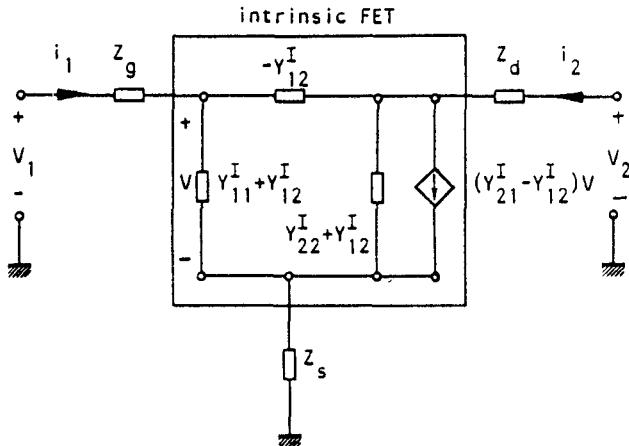

Fig. 4. Partitioning of a single-gate FET into intrinsic and parasitic elements. Parasitic elements are  $z_s = R_s + j\omega L_s$ ,  $z_g = R_g + j\omega L_g$ , and  $z_d = R_d + j\omega L_d$ .

nience of the reader their expression is rewritten:

$$\text{MAG} \approx \left( \frac{f_T}{f} \right)^2 \left/ \left( 4G_{ds} \left( R_i + R_s + R_g + \frac{\omega_T L_s}{2} \right) + 2\omega_T C_{dg} (R_i + R_s + 2R_g + \omega_T L_s) \right) \right. \quad (9)$$

where

$$\omega_T = 2\pi f_T = \frac{g_m}{C_{gs} + C_{dg}}. \quad (10)$$

Their work also includes a noise analysis, and important steps in the fabrication process of the FET are clarified.

### III. NEW METHOD OF ANALYSIS

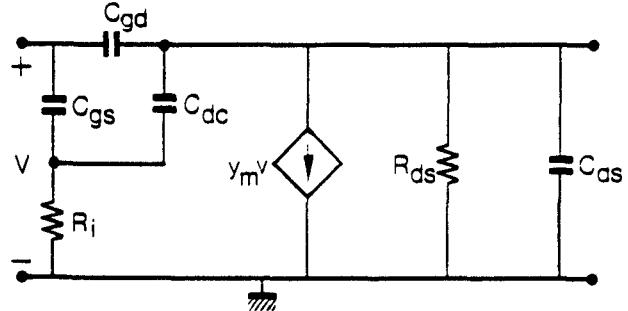

There is a need for device designers to be able to explore the benefits of changing the physical layout of standard compound FET's, e.g. in order to increase the power-handling capability or cutoff frequency. A physical device may be described by an equivalent circuit representation. Therefore, the benefits may be studied by means of basic circuit theory. An accurate formulation should use a realistic circuit description where elements representing the physical processes responsible for device operation should be present. To fulfill these basic requirements the complete circuit topology of Fig. 4 is used and the corresponding intrinsic equivalent circuit is shown in Fig. 5. Several popular circuit models are obtained by deleting elements from this general circuit description.

To obtain a compact and a manageable notation, it is assumed that the  $S$  parameters are transformed to the corresponding two-port impedance parameters. A more detailed description, explaining the advantages of using a circuit description in terms of  $z$  and  $y$  parameters, can be found in [10]. Furthermore, signal levels are assumed to be small enough to make linear analysis valid.

Several measures of gain, for example power gain ( $G_p$ ), available gain ( $G_a$ ), maximum available gain (MAG), maximum stable gain (MSG), Mason's gain ( $U$ ), and current gain ( $A_i$ ), all with their respective definitions, are impor-

Fig. 5. Intrinsic equivalent circuit  $y_m = g_m \exp(-j\omega\tau)$ .

tant in the design of both complete amplifiers and FET's. However, to approach the concept of gain partitioning,  $U$  and  $A_i$  are used. Their corresponding unity gain frequencies,  $f_{\max}$  and  $f_\tau$ , are distinct indicators of high-frequency performance.

Important conditions when mathematically formulating the new method of analysis are as follows:

- $U$  and MAG definitions of  $f_{\max}$  are equivalent. A proof can be found in [5]. Analysis should use the quantity  $U$  rather than MAG because analysis that makes use of MAG becomes too complicated.

- There should be partitioning of  $U$  and  $A_i$  in active and parasitic elements.

- The partitioning procedure should try to describe the interaction of parasitic elements and intrinsic elements in real- and/or complex-valued functions in such a way that the corresponding parasitic circuit elements are coefficients in these functions.

#### A. Partitioning of Mason's Gain, $U$

A partitioned expression of Mason's gain may be derived as (see Appendix I)

$$U = \frac{U_i}{1 + U_i(p_s + p_{g,d})} \quad (12)$$

where  $U_i$  characterizes the intrinsic element part and  $p_s$  and  $p_{g,d}$  are both parasitic functions. Their relationships to the impedance parameters are

$$U_i = \frac{|z_{21}^i - z_{12}^i|^2}{4\{r_{11}^i r_{22}^i - r_{21}^i r_{12}^i\}} \quad (13)$$

$$p_s = \frac{4R_s(r_{11}^i + r_{22}^i - r_{21}^i - r_{12}^i)}{|z_{21}^i - z_{12}^i|^2} \quad (14)$$

$$p_{g,d} = \frac{4(R_g(r_{22}^i + R_d + R_s) + R_d(r_{11}^i + R_s))}{|z_{21}^i - z_{12}^i|^2} \quad (15)$$

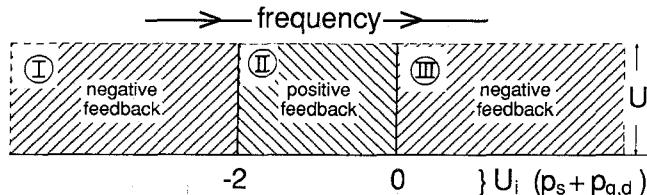

where  $r_{kl}^i$  is the real part of  $z_{kl}^i$ . The parasitic functions possess the following properties:

$$p_s = \begin{cases} 0 & \text{for } R_s = 0 \\ < 0 & \text{for } 0 < f \leq f_s; R_s \neq 0 \\ > 0 & \text{for } f > f_s; R_s \neq 0 \end{cases}$$

Fig. 6. Possible feedback regions of Mason's gain.

where  $f_s$  is a frequency that can be located high in the millimeter-wave region and

$$p_{g,d} = \begin{cases} 0 & \text{for } R_g = R_d = 0 \\ > 0 & \text{for all frequencies.} \end{cases}$$

This makes it possible to illustrate some general properties of (12) (see Fig. 6). It is possible, as frequency increases from left to right along the abscissa, to transit regions of negative feedback  $\rightarrow$  positive feedback  $\rightarrow$  negative feedback, referred to Mason's gain,  $U$ . The various feedback regions shown in Fig. 6 explain why  $U$  can sometimes show a resonance in the gain-frequency characteristic or merely a  $-6$  dB/octave slope in frequency performance.

It is important to note that a transistor can also have characteristics located only in one or two regions as the frequency varies. To examine this, we take the denominator of (12),

$$U_i(p_s + p_{g,d}) + 1 \quad (16)$$

and see that when

$$U_i(p_s + p_{g,d}) = -1 \quad (17)$$

Mason's gain,  $U$ , is in resonance. The frequency for which (17) is fulfilled is hence a critical parameter. From this it is clear that if low-frequency values are satisfied by

$$U_i(p_s + p_{g,d}) \leq -1 \quad (18)$$

or

$$U_i(p_s + p_{g,d}) > -1 \quad (19)$$

then the resulting gain-frequency characteristics are different in nature. If (18) is satisfied,  $U$  is resonant at some frequency and we have a gain slope of  $-12$  dB/octave after the complex pole pair. In general, (18) suggests that if the left-hand side of (18) is less than  $-2$  at low frequencies,  $U$  passes through all three feedback regions. On the other hand, if (19) is satisfied,  $U$  can pass through two feedback regions and show a gain slope of  $-6$  dB/octave at low frequencies and  $-9$  dB/octave at high frequencies before cutoff,  $f_{\max}$ . This is illustrated in subsection III-B.

It would be instructive for the reader if (17)—Mason's gain in resonance—could be related to a more common nomenclature. In fact, (17) is closely related (not mathematically equivalent) to another formulation that uses the scattering parameters and the stability factor, namely the transition from maximum stable gain (MSG) to maximum available gain (MAG). Since there is a loss of  $-3$  dB/

TABLE I

TRANSISTOR DATA USED TO ILLUSTRATE FEEDBACK REGIONS

| Device                                    | T1           | T2           | T3            |

|-------------------------------------------|--------------|--------------|---------------|

| Parameter (intrinsic)                     |              |              |               |

| $R_i[\Omega]$                             | 7.32         | 7.32         | 7.32          |

| $R_{ds}[\Omega]$                          | 206.4        | 206.4        | 206.4         |

| $g_m[\text{mS}]$                          | 57.2         | 57.2         | 57.2          |

| $\tau[\text{ps}]$                         | 3.17         | 3.17         | 3.17          |

| $C_{gs}[\text{pF}]$                       | 0.287        | 0.287        | 0.287         |

| $C_{ds}[\text{pF}]$                       | 0.082        | 0.082        | 0.082         |

| $C_{dg}[\text{pF}]$                       | 0.029        | 0.029        | 0.029         |

| $C_{dd}[\text{pF}]$                       | 0.010        | 0.010        | 0.010         |

| Parameter (parasitic)                     |              |              |               |

| $R_g[\Omega]$                             | 4.0          | 2.0          | 8.0           |

| $R_d[\Omega]$                             | 2.0          | 8.0          | 4.0           |

| $R_s[\Omega]$                             | 8.0          | 4.0          | 2.0           |

| $f_{\max}[\text{GHz}]$                    | $\approx 53$ | $\approx 44$ | $\approx 39$  |

| Frequency in GHz when $ p_s  =  p_{g,d} $ | 31.5         | 9.1          | not $\exists$ |

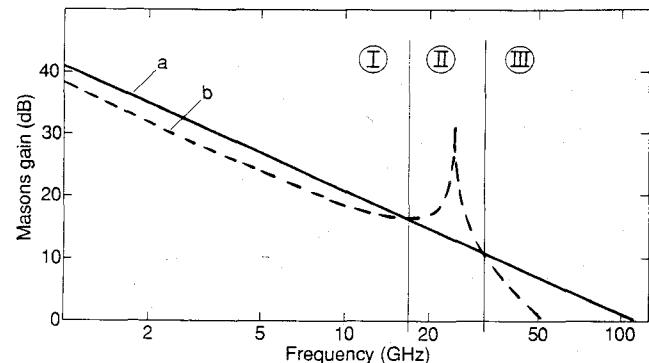

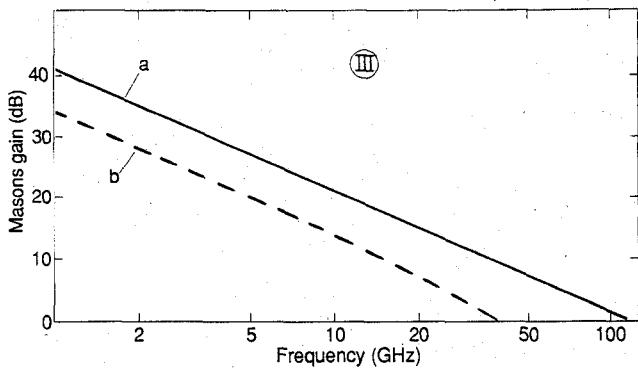

Fig. 7. Mason's gain for transistor T1. a: intrinsic gain  $U_i$ ; b: total gain  $U$ .

octave of the gain-frequency response at the transition MSG  $\rightarrow$  MAG, it can be understood that the corresponding frequency for the transition is critical, in order to obtain a maximized cutoff frequency,  $f_{\max}$ .

For the case where network parameters of an active device satisfy (19) for all frequencies, it has not been possible to identify a relationship between  $U$  and the transition MSG  $\rightarrow$  MAG.

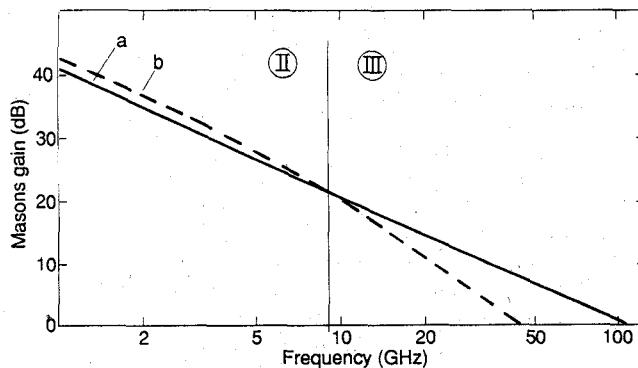

### B. Numerical Results for Mason's Gain

In this subsection we clarify the theory with numerical examples. Transistor data are given in Table I and the corresponding gain-frequency characteristics are shown in Figs. 7–10. For clarity, we show each transistor's gain-frequency characteristics in one figure. This simplifies the illustration of the various feedback regions. Note here that transistor T1 passes through all three regions, transistor T2 passes through two regions, and transistor T3 has characteristics located only in one region. Note

Fig. 8. Mason's gain for transistor T2. *a*: intrinsic gain  $U_i$ ; *b*: total gain  $U$ .

Fig. 9. Mason's gain for transistor T3. *a*: intrinsic gain  $U_i$ ; *b*: total gain  $U$ .

that the element combination  $R_g + R_s + R_d = \text{const.}$  for all three transistors.

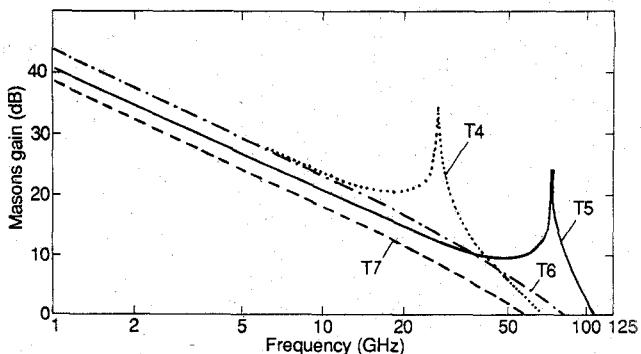

Circuit models with the topology of Fig. 4 have been developed for various FET's, yielding the element values of Table II. Transistors T4 and T5 both show a resonance in the gain-frequency response and have different cutoff frequencies. Their gain-frequency characteristics are located in all three feedback regions. Transistors T6 and T7 show both a gain slope of  $-6 \text{ dB/octave}$  at low frequencies and a  $-9 \text{ dB/octave}$  at high frequencies before cutoff,  $f_{\max}$ . Their gain-frequency characteristics are located only in region III. This indicates that if a realistic prediction of high-frequency performance is desired, extrapolations based upon a  $-6 \text{ dB/octave}$  gain slope are not correct.

#### IV. PARTITIONING OF CURRENT GAIN, $A_i$

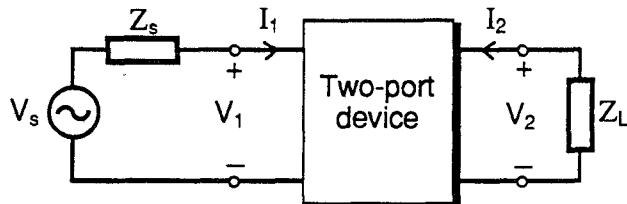

A high cutoff frequency,  $f_r$ , in a transistor indicates that it should be useful for integrated logic applications. A convenient way to examine this is to study the current drive capability of the device in question. The current gain of a two-port network is defined as the ratio of output current  $I_2$  to input current  $I_1$  (Fig. 11):

$$A_i = \frac{I_2}{I_1}. \quad (20)$$

Let the two-port device be characterized by a set of

Fig. 10. Mason's gain for the real transistors T4, T5, T6, and T7.

impedance parameters, then it can be shown that the current gain is given by

$$A_i = \frac{-z_{21}}{z_{22} + z_L} \quad (21)$$

and if  $z_{22} \neq 0$ ,  $A_i$  may be expressed in terms of hybrid parameters:

$$A_i = \frac{h_{21}}{1 + h_{22} z_L}. \quad (22)$$

For the special case where  $z_L = 0$ ,  $A_i$  is called the short-circuit current gain and is often just denoted as  $h_{21}$ .

Here, we consider the general case, with  $z_L \neq 0$ . By using the circuit topology shown in Fig. 4, a partitioned current gain expression may be derived as (see Appendix II)

$$A_i = \frac{(1+a)h_{21}^i}{1-bh_{21}^i} \quad (23)$$

where

$$a = z_s / z_{21}^i \quad (24)$$

$$b = (z_s + z_d + z_L) / z_{21}^i \quad (25)$$

$$h_{21}^i = -z_{21}^i / z_{22} \quad (26)$$

and  $h_{21}^i$  denotes the intrinsic current gain.

#### Interaction of Circuit Elements

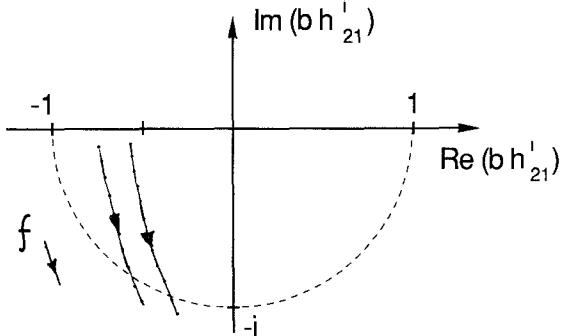

In this subsection we present an alternative way of studying the interaction between circuit elements, one different from the analysis applied to Mason's gain in subsection III-A. In this alternative approach we study the denominator of (23), giving particular attention to whether or not the equation  $bh_{21}^i = 1$  is satisfied at any frequency of operation. In fact, it can be shown that  $bh_{21}^i \neq 1$  for all frequencies. The proof is given below.

*Proof:* We want to prove that

$$bh_{21}^i \neq 1 \quad \forall \text{ frequencies}. \quad (27)$$

One way to show this is to formulate a proof based on contradiction, i.e., to prove instead that

$$bh_{21}^i = 1 \quad (28)$$

TABLE II

TRANSISTOR DATA FROM REAL DEVICES (†AFTER TREW [4])

| Device Source                      | T4<br>Feng [11]   | T5<br>Maki [12] | T6<br>Lau [13] | T7<br>Niclas [14] |

|------------------------------------|-------------------|-----------------|----------------|-------------------|

| Structure                          | 0.3×150 μm        | 0.25×60 μm      | 0.5×100 μm     | 0.35×200 μm       |

| Type                               | MESFET            | MESFET          | MESFET         | MESFET            |

| Parameter (intrinsic)              |                   |                 |                |                   |

| $R_s[\Omega]$                      | 0.94              | 2.69            | 2.13           | 3.3               |

| $R_{ds}[\Omega]$                   | 258               | 556             | 440            | 290               |

| $g_m[\text{mS}]$                   | 25.8              | 15.2            | 26.0           | 30.0              |

| $r[\text{ps}]$                     | 3.0               | 1.25            | 0              | 1.2               |

| $C_{gs}[\text{pF}]$                | 0.147             | 0.071           | 0.104          | 0.184             |

| $C_{ds}[\text{pF}]$                | 0.05              | 0.025           | 0.020          | 0.010             |

| $C_{dg}[\text{pF}]$                | 0.009             | 0.001           | 0.016          | 0.013             |

| $C_{dc}[\text{pF}]$                | 0.03 <sup>†</sup> | 0.011           | 0.003          | 0.047             |

| Parameter (parasitic)              |                   |                 |                |                   |

| $R_g[\Omega]$                      | 2.9               | 1.46            | 2.98           | 6.4               |

| $R_d[\Omega]$                      | 2.39              | 6.7             | 6.55           | 1.5               |

| $R_s[\Omega]$                      | 2.39              | 4.55            | 6.05           | 0.15              |

| $f_{\max}[\text{GHz}]$             | 66                | 103.5           | 79.5           | 56                |

| Freq. GHz when $ p_s  =  p_{g,d} $ |                   |                 |                |                   |

|                                    | 26.5              | 71.5            | not $\exists$  | not $\exists$     |

| Feedback regions                   | I → III           | I → III         | III            | III               |

Fig. 11. Terminated two-port network used to illustrate current gain definition.

cannot be satisfied with positive circuit elements. Thus, (28) can be manipulated into the equivalent form

$$\frac{z_{22}^i}{z_s + z_d + z_L} = -1. \quad (29)$$

Let  $z_{22}^i = r_{22}^i + jx_{22}^i$  and  $z_s + z_d + z_L = r_{\text{den}} + jx_{\text{den}}$ . Equation (29) can then be expressed as

$$\frac{r_{22}^i r_{\text{den}} + x_{22}^i x_{\text{den}} + j(r_{\text{den}} x_{22}^i - r_{22}^i x_{\text{den}})}{r_{\text{den}}^2 + x_{\text{den}}^2} = -1. \quad (30)$$

Restricting the imaginary part of (30) to be equal to zero gives

$$\frac{r_{\text{den}}}{x_{\text{den}}} = \frac{r_{22}^i}{x_{22}^i}. \quad (31)$$

Inserting (31) in (30), we get

$$\frac{r_{\text{den}}}{r_{22}^i} \cdot \frac{(r_{22}^i)^2 + (x_{22}^i)^2}{r_{\text{den}}^2 + x_{\text{den}}^2} = -1. \quad (32)$$

Fig. 12. Typical set to curves characterizing the complex function  $bh_{21}^i$ .

Equation (32) cannot be satisfied since both  $r_{\text{den}} \geq 0$  and  $r_{22}^i \geq 0$  for all frequencies. Q.E.D.

In addition, it is quite instructive to give some graphical illustrations. Numerical simulations result in the frequency characteristics shown in Fig. 12. These characteristics are typical. It is clear that the frequency dependence of the complex function  $bh_{21}^i$  does not approach the point where its value is unity.

As the frequency increases, the complex function  $bh_{21}^i$  departs from the particular solution  $bh_{21}^i = 1$ . Thus, it is clear that the interaction of the two parts cannot force the transfer function of (23) into a region of positive feedback, as in the case for Mason's gain. Any inclusion of parasitic circuit elements degrades the intrinsic gain-frequency response. Therefore, parasitic circuit elements should be minimized, not optimized, to obtain higher cutoff frequencies.

## V. DISCUSSION

The speed of active components such as FET's and bipolar transistors is limited by both internal and external circuit components. It is usually recognized among device designers and microwave engineers that in first-order design it is important to maximize  $g_m$  and to minimize  $C_{gs}$ . Among second-order parameters it is recognized that the internal time delay,  $\tau$ , is the factor that most limits the speed of the internal components and should therefore be minimized. External components that affect the speed are low-resistance ohmic contacts formed under the drain and source metallization and additional parasitic drain and source resistances. Associated gate resistance and fringing capacitances are other components that affect the high-frequency response.

By using a realistic circuit description that takes into account the series resistances associated with the three terminals of the device, the approach has been applied to two important gain measures, Mason's gain ( $U$ ) and current gain ( $A_i$ ). The concept of gain partitioning makes it possible to simultaneously study the interaction of active and parasitic circuit elements. This need cannot be satisfied by using such modern commercial CAD software as TOUCHSTONE and COMPACT.

By using the element combination

$$R_g + R_s + R_d = \text{constant} \quad (33)$$

for the three transistors T1–T3 in Table I, it was illustrated that these transistors have different cutoff frequencies. This means that the element sum should not be minimized to obtain a maximized cutoff frequency,  $f_{\max}$ . It does indicate that the element sum should be optimized with the intrinsic part to produce a maximized cutoff frequency. This result is interesting since first-order theory indicates that the parasitic circuit elements should be minimized to provide the maximum  $f_{\max}$ . By calculating this sum for the real devices (data given in Table II), we observe that it is not the minimum sum that produces the highest  $f_{\max}$  of these transistors.

## VI. CONCLUSION

A powerful gain-partitioning approach that exploits the properties of various power measures has been presented. Previous implications by, among others, Trew [3] that the device structure of a compound transistor may be optimized to obtain a tuned high-frequency response have been verified. We have formulated the method by using concepts from basic circuit theory. Results presented here show that the requirements of maximizing the cutoff frequencies  $f_{\max}$  and  $f_{\tau}$  of a transistor are different in nature. Results indicate that minimized parasitic circuit elements maximize  $f_{\tau}$ . A maximized  $f_{\max}$ , on the contrary, may be obtained if the interaction of parasitic and intrinsic circuit elements fulfills certain conditions. This means that parasitic circuit elements should be optimized, not minimized, in conjunction with the intrinsic element part of the transistor. The method presented here should be considered for use in conjunction with software that

can specify the physical structure required to realize those circuit elements.

## APPENDIX I PARTITIONED EXPRESSION OF MASON'S GAIN

The two-port  $z$  parameters of the network shown in Fig. 4, can be derived as

$$z_{11} = z_s + z_g + y_{22}^i / \Delta y^i \quad (A1)$$

$$z_{12} = z_s - y_{12}^i / \Delta y^i \quad (A2)$$

$$z_{21} = z_s - y_{21}^i / \Delta y^i \quad (A3)$$

$$z_{22} = z_d + z_s + y_{11}^i / \Delta y^i \quad (A4)$$

where

$$\Delta y^i = y_{11}^i y_{22}^i - y_{12}^i y_{21}^i \quad (A5)$$

and the superscript  $i$  denotes the intrinsic part of the device. Now, let the real part of the intrinsic device be denoted by  $\text{Re}(z_{lm}^i) = r_{lm}^i$ ,  $l, m = 1, 2$ . Mason's gain may be written

$$U = \frac{|z_{21}^i - z_{12}^i|^2}{4[(R_g + R_s + r_{11}^i)(R_d + R_s + r_{22}^i) - (R_s + r_{12}^i)(R_d + r_{21}^i)]} \\ = \frac{U_i}{1 + U_i(p_s + p_{g,d})} \quad (A6)$$

where

$$U_i = \frac{|z_{21}^i - z_{12}^i|^2}{4[r_{11}^i r_{22}^i - r_{12}^i r_{21}^i]} \quad (A7)$$

$$p_s = \frac{4R_s(r_{11}^i + r_{22}^i - r_{12}^i - r_{21}^i)}{|z_{21}^i - z_{12}^i|^2} \quad (A8)$$

$$p_{g,d} = \frac{4[R_g(r_{22}^i + R_s + R_d) + R_d(r_{11}^i + R_s)]}{|z_{21}^i - z_{12}^i|^2}. \quad (A9)$$

## APPENDIX II DERIVATION OF THE PARTITIONED CURRENT GAIN EQUATION

The current gain,  $A_i$ , is defined as the ratio of output current  $I_2$  to the input current  $I_1$  (Fig. 11); so that

$$A_i = \frac{I_2}{I_1}. \quad (A10)$$

When an impedance  $z_L$  is connected across the output, as shown in Fig. 11, the conditions existing at this port become constrained by the relation

$$V_2 = -I_2 z_L. \quad (A11)$$

In terms of the  $z$  parameters, we have, for the two-port network,

$$V_1 = z_{11} I_1 + z_{12} I_2 \quad (A12)$$

$$V_2 = z_{21} I_1 + z_{22} I_2. \quad (A13)$$

Eliminating now  $V_2$  between the two voltage equations above and then solving for the current gain, we obtain

$$A_i = \frac{-z_{21}}{z_{22} + z_L}. \quad (\text{A14})$$

Consider now the network topology shown in Fig. 4. The two-port  $z$  parameters can be derived as (see Appendix I)

$$z_{11} = z_s + z_g + y_{22}^i / \Delta y^i \quad (\text{A1})$$

$$z_{12} = z_s - y_{12}^i / \Delta y^i \quad (\text{A2})$$

$$z_{21} = z_s - y_{21}^i / \Delta y^i \quad (\text{A3})$$

$$z_{22} = z_d + z_s + y_{11}^i / \Delta y^i \quad (\text{A4})$$

where

$$\Delta y^i = y_{11}^i y_{22}^i - y_{12}^i y_{21}^i \quad (\text{A5})$$

and the superscript  $i$  denotes the intrinsic element part of the device.

To obtain a compact notation, let us use the relationship between the impedance and admittance parameters:

$$z_{11}^i = y_{22}^i / \Delta y^i \quad (\text{A15})$$

$$z_{12}^i = -y_{12}^i / \Delta y^i \quad (\text{A16})$$

$$z_{21}^i = -y_{21}^i / \Delta y^i \quad (\text{A17})$$

$$z_{22}^i = y_{11}^i / \Delta y^i. \quad (\text{A18})$$

Thus, we obtain a current gain equation that can be written

$$A_i = \frac{-(z_s + z_{21}^i)}{z_d + z_s + z_L + z_{22}^i}. \quad (\text{A19})$$

This total current gain equation can now be manipulated to form an intrinsic current gain part and a parasitic current gain part. Depending upon the approach used, different analytical expressions can be obtained. However, it has been found that the procedure described below is well suited to illustrate the current gain partitioning approach. (It is numerically efficient and a side benefit is that the notation resembles that of classical feedback theory.)

Thus, the current gain may be written

$$A_i = \frac{-z_{21}^i (1 + z_s / z_{21}^i)}{z_{22}^i (1 + (z_d + z_s + z_L) / z_{22}^i)} \quad (\text{A20})$$

and finally arranged to the form

$$A_i = \frac{(1 + a) h_{21}^i}{1 - b h_{21}^i} \quad (\text{A21})$$

where

$$a = z_s / z_{21}^i \quad (\text{A22})$$

$$b = (z_s + z_d + z_L) / z_{21}^i \quad (\text{A23})$$

$$h_{21}^i = -z_{21}^i / z_{22}^i. \quad (\text{A24})$$

## REFERENCES

- [1] G. W. Wang, M. Feng, C. L. Lau, C. Ito, and T. R. Lepkowski, "0.25  $\mu\text{m}$  gate millimeter-wave ion implanted GaAs MESFET," *IEEE Electron Device Lett.*, vol. 10, pp. 186-188, 1989.

- [2] G. W. Wang, M. Feng, C. L. Lau, C. Ito, and T. R. Lepkowski, "Ultra high frequency performance of submicrometer gate ion-implanted GaAs MESFET's," *IEEE Electron Device Lett.*, vol. 10, pp. 206-208, 1989.

- [3] R. J. Trew, "Equivalent circuits for high frequency transistors," in *Proc. IEEE / Cornell Conf. Advanced Concepts in High Speed Semiconductor Devices and Circuits*, 1987, pp. 199-208.

- [4] R. J. Trew, "Millimetre-wave performance of state-of-the-art MESFET, MODFET and PBT transistors," *Electron. Lett.*, vol. 23, no. 4, pp. 149-151, 1987.

- [5] H.-O. Vickes, "Comparison of the gain and frequency performance of compound field-effect transistors," Division of Network Theory, Tech. Rep. TR8805, Chalmers University of Technology, Gothenburg, Sweden.

- [6] P. Wolf, "Microwave properties of Shottky-barrier field-effect transistors," *IBM J. Res. Develop.*, vol. 14, pp. 125-141, 1970.

- [7] S. Ohkawa, K. Suyama, and H. Ishikawa, "Low noise GaAs field-effect transistors," *Fujitsu Sci. Tech. J.*, pp. 151-173, Mar. 1975.

- [8] H.-O. Vickes, "Note on unilateral power gain as applied to submicrometre transistors," *Electron Lett.*, vol. 24, no. 24, pp. 1503-1505, 1988.

- [9] S. J. Mason, "Power gain in feedback amplifiers," *IRE Trans. Circuit Theory*, vol. CT-1, pp. 20-25, June 1954.

- [10] H.-O. Vickes, "Determination of intrinsic FET parameters using circuit partitioning approach," *IEEE Trans. Microwave Theory Tech.*, vol. 39, pp. 363-366, Feb. 1991.

- [11] M. Feng, H. Kanber, V. K. Eu, E. Watkins, and L. R. Hackett, "Ultrahigh frequency operation of ion-implanted GaAs metal-semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 44, no. 2, Jan. 15, 1984.

- [12] D. W. Maki, J. M. Schellenberg, H. Yamasaki, and L. C. T. Liu, "A 69 GHz monolithic FET oscillator," in *IEEE 1984 Microwave and Millimeter-Wave Monolithic Circuits Symp. Dig.*, June 3-4, 1984, pp. 62-66.

- [13] C. L. Lau *et al.*, "Half-micrometer gate-length ion-implanted GaAs MESFET with 0.8 dB noise figure at 16 GHz," *IEEE Electron Device Lett.*, vol. 10, no. 9, Sept. 1989.

- [14] K. B. Niclas and R. Pereira, "On the design and performance of a 6-18 GHz three-tier matrix amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 1069-1077, July 1989.

**Hans-Olof Vickes** (S'88) was born in Malung, in the province of Dalarna, Sweden, in 1954. He received the degrees of Civilingenjör (M.Sc.), Tekn. Licentiat, and Ph.D. in 1982, 1988, and 1990, respectively, from the Electrical Engineering Department of Chalmers University of Technology, Gothenburg, Sweden. His doctoral thesis dealt with microwave and millimeter-wave FET's and noise parameter measurements.

In October 1990 he joined the Space Department at Ericsson Radar Electronics, Mölndal, Sweden. His current research activities concern nonlinear modeling, CAD techniques, and measurement techniques.